Architettura Elaboratori

PROF: Cattuto

Logica di Boole

AND ha precedenza su OR

Leggi di DeMorgan

Una funzione booleana associa un valore boolean a ciascuna delle 2^n configurazioni A partire da una tabella di verita' o Binary Decision Diagrams:

- FND Formula Normale Disgiuntiva Quindi somme tra prodotti di lettere

- FNC Formula Normale Congiuntiva Quindi Produttoria tra sommatorie di lettere

Aritmetica Binaria

Numeri in basi diverse e conversioni

Binario

Modulo e segno

- Riserva il bit piu' significativo per il segno e rappresenta normalmente il numero binario come modulo sui bit rimanenti

- Anche qui abbiamo +0 e -0

Eccesso 2^n

Complemento a 1

Intervallo di rappresentazione: [-2^n+1,2^n-1] ha una doppia rappresentazione per lo 0: tutti 0 o tutti 1

- Positivi numero binario

- Negativi numero binario invertito

Complemento a 2

Intervallo di rappresentazione: [2^n,2^n-1] rispetto al C1 risolve la doppia rappresentazione per lo 0

- Positivi numero binario

- Negativi numero binario invertito + 1

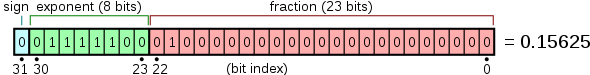

Standard IEEE 754

Sviluppato nel 1985

~~~~~~~~~~~~~~~~~

Standard per la rappresentazione in float point/virgola mobile

Precisioni- Singola 32bit

- Doppia 64bit

- Estesa 128bit

Esponente- calcolato in eccesso 127

Mantissa- valore

normalizzato(1,… la parte intera e' sottointesa)

- valore

Ci sono dei valori speciali che indicano dei particolari stati

- Non Normalizzato 0 esponente, mantissa != 0

- 0 0 esponente, 0 mantissa

- Infinito 1111… esponente, 0 mantissa

- Not A Number 1111… esponente, mantissa != 0

Questo in quanto i reali allo la potenza dell'infinito: avremo aree non rappresentabili di under e over flow e anche numeri non rappresentabili perche' tra due numeri rappresentabili, allora si effettura' una stima.

| Segno | Esponente | Mantissa | (Precisione Singola) |

|---|---|---|---|

| 1 | 8 | 23 | Numero di Bit |

Codifiche

-

Caratteri

- ASCII

- UNICODE

- UTF-8

-

Suoni e Immagini

Campionamento del segnale- discretizzando colori nello spazio

- discretizzando suoni nel tempo

Livelli di Architettura di un Elaboratore

I livelli sono astrazioni che permettono lo sviluppo di software ad alto livello

- un

compilatorepuo' ottimizzare ma solo per una CPU e non agisce istruzione per istruzione in runtime - il passaggio da un livello all’altro e' possibile con l'

interpretazione(instruzione per istruzione)NBJava e' una soluzione mista:- Compilatore –> bytecode JVM –> Interprete specifico

I livelli sono:

0 - Logico digitale

- porte

- memorie

-

Circuiti Digitali

Elemento base:

Transistor- 1 -> il transistor di comporta come una resistenza infinita

- 0 -> il transistor si comporta come un filo

2 transistor in serie implementano un NAND 2 transistor in parallelo implementano un NOR 1 implementa un invertitore 8 implementano uno XOR

- I

Circuiti Integratio chip (IC)- SSI small scale integrated

- MSI

- LSI

- VLSI

-

Dipendono da una

funzioned’entrata- L’output dipende solo dall’input

-

Dipendono da una

funzioned’entrata e da unostato

-

Registri

flip-flop dipo D temporizzati indirizzati attraverso decoder o bit di attivazione

- CS - Chip Select

- RD - Read

- OE - Output Enabled

Organizzati a indirizzi di n parole da m bit

le uscite degli indirizzi passano per un multiplexer che passa il dato voluto in uscita

Possiedono un controllo prima dell’uscita: registro con buffer (3 stati: 0,1, scollegato)

-

Memorie

Insieme di celle, ampiezza di parola 1B/4B/8B

Ordinamento:

- Litle endian

- Little End First, sx <– dx

- Bin endian

-

Big End First, sx –> dx

-

Static RAM

- veloci

- poca memoria

- flip-flop tipo d

-

Dynamic RAM

- lente

- grandi capacita'

- transistor con condensatori

-

ROM

- sola lettura

-

- Litle endian

-

Bus

linee di

- controllo

- evitano che i dispositivi accedano allo stesso momento al Bus

- dati

- indirizzi

La larghezza del bus dipende dall’architettura, in Mic-1 si tratta di Bus da 32 bit

Tipi di Bus

- Sistema

- Interni alla CPU

- SCSI esterni

La CPU comunica con la cache e la memoria in caso di Miss (vedi

Principio di Localita' del Codice)I dispositivi possone essere:

- attivi | master

- passivi | slave

o entrambi (CPU): transceiver

Principi di progettazione:

- larghezza

- arbitraggio

- funzionamento

- multiplexed bus

- bus sincrono o asincrono

- Sincrono

- ogni operazione ha durata conosciuta

- interi di ciclo

- semplice realizzare uno slave

- la sua velocita' dipende dal dispositivo piu' lento

- ogni operazione ha durata conosciuta

- Asincrono

- la velocita' dipende esclusivamente dalla coppia master-slave

- ogni operazione ha la durata strettamente necessaria

- e' necessario implementare una full-handshake per la sincronizzazione di slave e master

- 4 segnali di controllo

- Sincrono

- controllo

1 - Microarchitettura

- ALU

- Microprogramma

-

composto da:

- Data Path

- Control Unit

2 - Instruction Set Architecture : ISA

- linguaggio macchina

- opcode

3 - Sistema Operativo

- linguaggio ISA

- Input/Output

- gestisce i processi

4 - Assembly

- Istruzioni simboliche